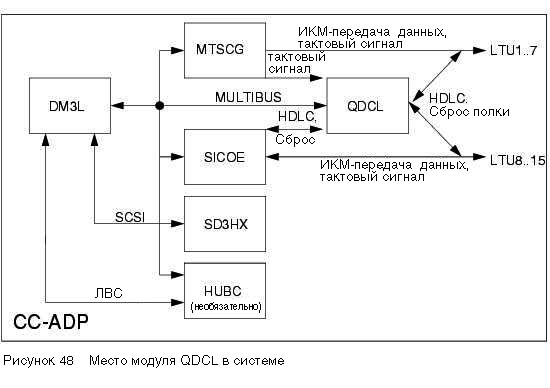

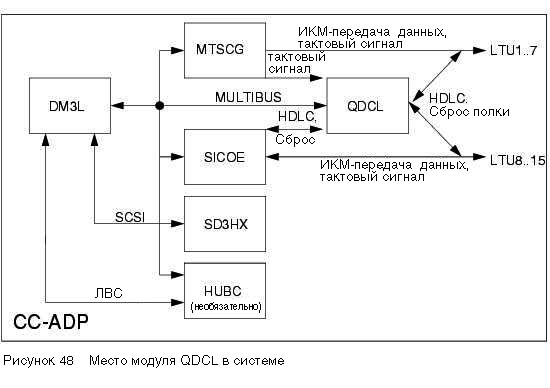

QDCL - счетверенный канал передачи данных

Модуль QDCL представляет собой интерфейс между периферией и центральным процессором данных DP (модулем DP4L или DM3L) системы 350 E.

Этот модуль обслуживает 16 двунаправленных каналов HDLC

(15 LTU + 1 SICOE). Связь с процессором данных осуществляется через внешнее

двухпортовое ОЗУ (DPRe), благодаря чему обеспечивается независимый асинхронный доступ с процессора данных через многофункциональную шину Multibus, а также из модуля QDCL через локальную шину.

Для реализации такой концепции модуль QDCL делится на две части, одна из

которых относится к интерфейсу Multibus (центральный процессор данных CMP), а

вторая к интерфейсу связи HDLC с периферийными устройствами (линейный процессор

LP). Оба эти функциональных блока обмениваются данными через внутреннее

двухпортовое ОЗУ (DPRi).

Светодиодные индикаторы и кнопки

|

1 светодиод красного цвета (сигналы тревоги и состояние модуля). |

|

1 светодиод зеленого цвета (состояние модуля). |

|

Переключатель перезапуска CC (служит не для сброса, а для "мягкого" перезапуска CC). |

Компоновка основных элементов на печатной плате

Элементы модуля располагаются в соответствии с его логическим делением на CMP, LP, DPRe и DPRi.

Разъем печатной платы

Модуль QDCL оснащен разъемом SIPAC, содержащим 9 секций (SU) с общим количеством контактов до 344. .

Модуль QDCL использует 196 контактов, которые распределены по всем 9 секциям. Все эти контакты (включая проверочные) соединены с объединительной платой полки CCDAX.

Никаких дополнительных разъемов на передней панели

модуля нет.

Таблица 119. Разводка контактов разъема SIPAC модуля QDCL

|

|

4 E |

3 D |

2 C |

1 B |

0 A |

|

1 |

|

Не используется |

|

|

2 |

ADR0/ |

ADR1/ |

ОБЩ |

ADR2/ |

|

|

3 |

ADR3/ |

ADR4/ |

ADR5/ |

ADR6/ |

|

|

4 |

ADR7/ |

ADR8/ |

ADR9/ |

ADRA/ |

|

X1 |

5 |

ADRB/ |

ADRC/ |

ADRD/ |

ADRE/ |

|

|

6 |

ADRF/ |

ADR10/ |

ADR11/ |

ADR12/ |

|

|

7 |

ADR13/ |

ADR14/ |

ADR15/ |

ADR16/ |

|

|

8 |

ADR17/ |

BHEN/ |

ОБЩ |

|

|

|

9 |

|

|

|

|

|

|

10 |

+5 В |

+5 В |

+5 В |

|

|

|

1 |

DAT0/ |

DAT1/ |

DAT2/ |

DAT3/ |

|

|

2 |

DAT4/ |

DAT5/ |

|

DAT6/ |

|

|

3 |

DAT7/ |

DAT8/ |

DAT9/ |

DATA/ |

|

|

4 |

DATB/ |

DATC/ |

DATD/ |

DATE/ |

|

X2 |

5 |

DATF/ |

|

|

|

|

|

6 |

|

|

|

|

|

|

7 |

|

|

|

|

|

|

8 |

|

|

|

|

|

|

9 |

INIT/ |

|

|

|

|

|

10 |

NC |

+5 В |

|

|

|

|

1 |

|

|

|

|

|

|

2 |

|

ACTIV_O/ |

|

ACTIV_P/ |

|

|

3 |

|

|

|

|

|

|

4 |

|

CMP_THRQ/ |

LP_THRQ/ |

|

|

X3 |

5 |

|

|

|

TDI |

|

|

6 |

|

|

TRST/ |

|

|

|

7 |

|

TMS |

|

TDO |

|

|

8 |

TCK |

|

|

INH1/ |

|

|

9 |

|

CMP_TSTOUT |

|

LP_TSTOUT |

|

|

10 |

NC |

+5 В |

|

|

|

|

1 |

IORC/ |

IOWC/ |

MWTC/ |

MRDC/ |

|

|

2 |

|

XACK/ |

|

|

|

|

3 |

|

|

|

|

|

|

4 |

|

|

|

|

|

X4 |

5 |

|

|

|

|

|

|

6 |

|

|

|

|

|

|

7 |

|

|

|

|

|

|

8 |

INT5/ |

|

|

|

|

|

9 |

|

Не используется |

|

|

10 |

NC |

+5 В |

+5 В |

|

|

|

1 |

SHRES1P |

HDO1P |

|

HDI1P |

|

|

2 |

SHRES1N |

HDO1N |

|

HDI1N |

|

|

3 |

SHRES2P |

HDO2P |

|

HDI2P |

|

|

4 |

SHRES2N |

HDO2N |

|

HDI2N |

|

X5 |

5 |

|

|

|

|

|

|

6 |

SHRES3P |

HDO3P |

|

HDI3P |

|

|

7 |

SHRES3N |

HDO3N |

|

HDI3N |

|

|

8 |

SHRES4P |

HDO4P |

|

HDI4P |

|

|

9 |

SHRES4N |

HDO4N |

|

HDI4N |

|

|

10 |

|

+5 В |

+5 В |

|

|

|

1 |

|

Не используется |

|

|

2 |

SHRES5P |

HDO5P |

|

HDI5P |

|

|

3 |

SHRES5N |

HDO5N |

|

HDI5N |

|

|

4 |

SHRES6P |

HDO6P |

|

HDI6P |

|

X6 |

5 |

SHRES6N |

HDO6N |

|

HDI6N |

|

|

6 |

SHRES7P |

HDO7P |

|

HDI7P |

|

|

7 |

SHRES7N |

HDO7N |

|

HDI7N |

|

|

8 |

SHRES8P |

HDO8P |

|

HDI8P |

|

|

9 |

SHRES8N |

HDO8N |

|

HDI8N |

|

|

10 |

|

+5 В |

|

|

|

|

1 |

SHRES9P |

HDO9P |

|

HDI9P |

|

|

2 |

SHRES9N |

HDO9N |

|

HDI9N |

|

|

3 |

SHRES10P |

HDO10P |

|

HDI10P |

|

|

4 |

SHRES10N |

HDO10N |

|

HDI10N |

|

X7 |

5 |

|

|

|

|

|

|

6 |

SHRES11P |

HDO11P |

|

HDI11P |

|

|

7 |

SHRES11N |

HDO11N |

|

HDI11N |

|

|

8 |

SHRES12P |

HDO12P |

|

HDI12P |

|

|

9 |

SHRES12N |

HDO12N |

|

HDI12N |

|

|

10 |

|

+5 В |

|

|

|

|

1 |

SHRES13P |

HDO13P |

|

HDI13P |

|

|

2 |

SHRES13N |

HDO13N |

|

HDI13N |

|

|

3 |

SHRES14P |

HDO14P |

|

HDI14P |

|

|

4 |

SHRES14N |

HDO14N |

|

HDI14N |

|

X8 |

5 |

|

|

|

|

|

|

6 |

SHRES15P |

HDO15P |

|

HDI15P |

|

|

7 |

SHRES15N |

HDO15N |

|

HDI15N |

|

|

8 |

|

|

|

|

|

|

9 |

|

|

|

|

|

|

10 |

+5 В |

+5 В |

+5 В |

|

|

|

1 |

|

|

|

|

|

|

2 |

|

SCHDO |

|

SCHDI |

|

|

3 |

|

|

SCRES/ |

|

|

|

4 |

|

|

|

|

|

X9 |

5 |

|

|

|

|

|

|

6 |

|

|

|

|

|

|

7 |

|

|

|

|

|

|

8 |

|

|

|

CKA |

|

|

9 |

|

Не используется |

|

Цветовое кодирование |

Тип соединения |

|

С блоком питания. |

|

С процессором данных по шине Multibus 1. |

|

Интерфейс LTU (сброс HDLC и полки). |

|

Проверочное (сканирование контуров и проверка модуля). |

|

С модулем MTSCG (тактовые сигналы и сигналы активности). |

|

С модулем SICOE (HDLC и сброс). |

Для обозначения сигнальных контактов используется приведенная ниже схема.

|

Буквы P и N после названия симметричного сигнала обозначают положительную и отрицательную часть двухпроводного симметричного соединения. |

|

Косая черта (/) в конце названия сигнала указывает на то, что активному сигналу соответствует низкий потенциал. |

|

HDOx означает выход HDLC на одну из 15 полок LTU ( x = 1-15).

HDIx означает вход HDLC от одной из 15 полок LTU (x = 1-15). |

|

SHRESx означает выходной сигнал сброса одной из 15 полок LTU (x = 1 - 15). |

|

Буква 'T' в начале названия сигнала означает сигнал проверки интерфейса. |

|

Буквы 'SC' в начале названия означают сигнал интерфейса SICOE. |

|

NC = не соединен (предупреждает, что к этому

контакту может быть приложена часть напряжения,

подаваемого на другие разъемы этого же гнезда). |

ICN

ICN

ICN

ICN